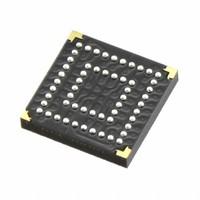

XC2C32A-4CP56C Overview 32 macrocells are present in the mobile phone network, which offer radio coverage from a high-power cell tower, antenna, or mast.The item is enclosed in a 56-LFBGA, CSPBGA package.The device is programmed with 33 I/O ports.It is programmed to terminate devices at 56.There is a BOTTOM terminal position on the electrical part in question.The device is powered by a voltage of 1.8V volts.It is recommended that the chip be packaged by Tray.Ensure its reliability by operating at 0°C~70°C TA.It is recommended to mount the chip by Surface Mount.FPGAs belonging to the CoolRunner II series contain this type of chip.With 56 pins programmed, the chip is ready to use.When using this device, REAL DIGITAL DESIGN TECHNOLOGY is also available.You can find its related parts in the XC2C32A.750 gates are used to construct digital circuits.If high efficiency is desired, the supply voltage should be kept at 1.8V.It is recommended that data be stored in ROMless.In this case, it is mounted by Surface Mount.The pins are 56.Initially, the maximum supply voltage (Vsup) is 1.9V.It is important to make sure that the maximum frequency is less than 323MHz.An elementary building block consists of 2logic elements/cells.

XC2C32A-4CP56C Features56-LFBGA, CSPBGA package

33 I/Os

The operating temperature of 0°C~70°C TA

56 pin count

56 pins

XC2C32A-4CP56C ApplicationsThere are a lot of Xilinx Inc.

XC2C32A-4CP56C CPLDs applications.

Digital systems

Portable digital devices

Handheld digital devices

Battery operated portable devices

Complex programmable logic devices

Digital designs

Field programmable gate

Address decoding

D/T registers and latches

Synchronous or asynchronous mode

| Factory Lead Time | 10 Weeks |

| Mount | Surface Mount |

| Mounting Type | Surface Mount |

| Package / Case | 56-LFBGA, CSPBGA |

| Number of Pins | 56 |

| Operating Temperature | 0°C~70°C TA |

| Packaging | Tray |

| Series | CoolRunner II |

| Published | 2001 |

| JESD-609 Code | e0 |

| Pbfree Code | no |

| Part Status | Active |

| Moisture Sensitivity Level (MSL) | 3 (168 Hours) |

| Number of Terminations | 56 |

| ECCN Code | EAR99 |

| Terminal Finish | Tin/Lead (Sn63Pb37) |

| Additional Feature | REAL DIGITAL DESIGN TECHNOLOGY |

| Terminal Position | BOTTOM |

| Terminal Form | BALL |

| Peak Reflow Temperature (Cel) | 240 |

| Supply Voltage | 1.8V |

| Terminal Pitch | 0.5mm |

| Time@Peak Reflow Temperature-Max (s) | 30 |

| Base Part Number | XC2C32A |

| Pin Count | 56 |

| Qualification Status | Not Qualified |

| Operating Supply Voltage | 1.8V |

| Supply Voltage-Max (Vsup) | 1.9V |

| Programmable Type | In System Programmable |

| Number of I/O | 33 |

| Memory Type | ROMless |

| Propagation Delay | 4 ns |

| Number of Logic Elements/Cells | 2 |

| Number of Gates | 750 |

| Max Frequency | 323MHz |

| Speed Grade | 4 |

| Output Function | MACROCELL |

| Number of Macro Cells | 32 |

| JTAG BST | YES |

| Voltage Supply - Internal | 1.7V~1.9V |

| Delay Time tpd(1) Max | 3.8ns |

| Length | 6mm |

| Height Seated (Max) | 1.35mm |

| Width | 6mm |

| RoHS Status | Non-RoHS Compliant |